# 12 - MOSFETS!

Name:

## In-Class Problems

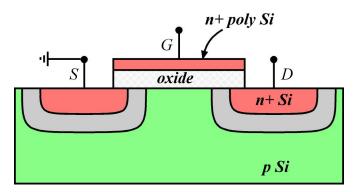

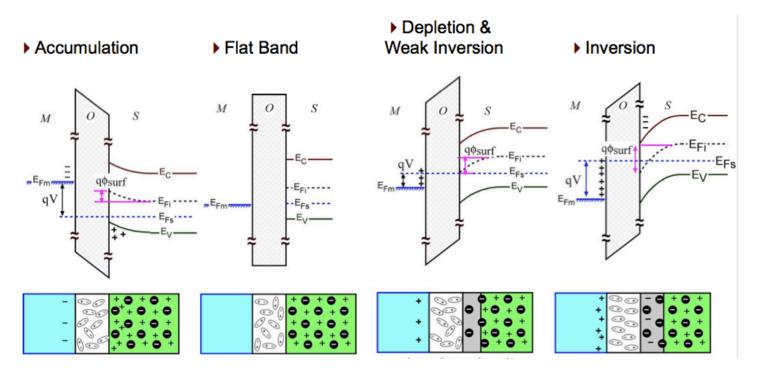

### (1) The band diagrams and device cross-section for an NMOS device are shown below.

(a) for the <u>NMOS</u> device, if we add a positive drain voltage, and apply no gate voltage why can't we get current to flow from drain to source?

(b) now, instead of just restating what you learned from the videos, lets test your basic understanding by having you redraw the diagrams below and at right for a <u>PMOS</u> device. Label them as 'inversion, accumulation, flat band, depletion' and... further label which one will be the most conductive and least conductive in terms of drain-to-source current.

(c) For this PMOS device, you would apply a negative voltage

to the gate to turn it on. You know that if you keep increasing drain voltage you will run into saturation (like pinchoff), therefore, what is the polarity (+ or -) of the drain voltage you would apply to PMOS?

(d) lastly, for the 'depletion' diagram, draw a plot of E-field vs. distance for the metal, oxide, depleted semiconductor, and un-depleted semiconductor portions.

Instructor – Prof. Jason Heikenfeld

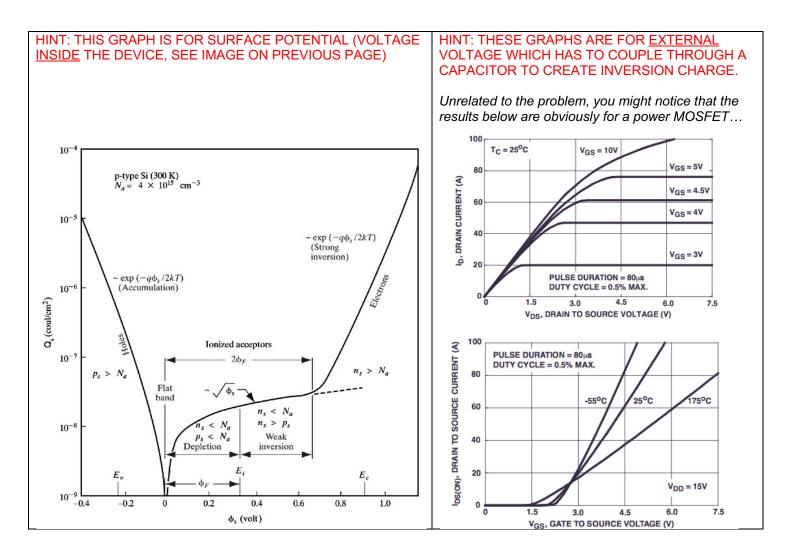

(2) Some multiple choice questions for NMOS. For the 1<sup>st</sup> few, remember that charge generation under the gate of a MOSFET follows either only depletion (dopant atoms) or Fermi-level shift type effects (carrier generation). Pick one answer for each. Do MORE than just look at the curves above, make sure you UNDERSTAND why as well!

(a) for accumulation, the charge increases with <u>surface potential</u> in a manner that is: linear / exponential / square root / quadratic.

(b) for depletion, the charge increases with <u>surface potential</u> in a manner that is: linear / exponential / square root / quadratic.

(c) for inversion, the charge increases with <u>surface potential</u> in a manner that is: linear / exponential / square root / quadratic.

(d) true or false, at threshold voltage you have already paid the maximum price (in terms of voltage) for depletion charge.

(e) true or false, if you increase substrate doping, you will have to shift the bands even more to get to threshold voltage

(f) true or false, the depletion region width maximizes at threshold voltage because you run out of dopant atoms to deplete

(g) true or false, at threshold voltage a square root function is taken over by an exponential function for charge generation

(h) true or false, inversion charge in the channel appears exponentially with external gate voltage (hint, Q=CV).

Page 2 of 4

# (3) Consider an <u>ideal</u> n-channel MOSFET on a p-Si substrate with the following characteristics (you may or may not need all the information provided below):

Na=10<sup>16</sup>/cm<sup>3</sup> Oxide thickness = 50 nm Area of gate = 1x1  $\mu$ m W<sub>m</sub>= 300 nm

$$\begin{split} \epsilon_{\text{SiE0}} &= 11.8 \; x \; 8.854 x 10^{\text{-14}} \; \text{F/cm} = 1.0 x 10^{\text{-12}} \; \text{F/cm} \\ \epsilon_{\text{oxide} \epsilon_0} &= 4 \; x \; 8.854 x 10^{\text{-14}} \; \text{F/cm} = 3.4 x 10^{\text{-13}} \; \text{F/cm} \\ \varphi_F &= 0.347 \; \text{eV} \end{split}$$

(a) Calculate the maximum charge per unit area that will appear under the gate.

(b) Calculate the gate capacitance per unit area.

(c) Calculate the threshold voltage for this device.

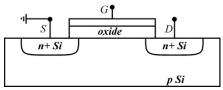

### (4) Some more EASY multiple choice questions for an ideal n-channel MOSFET device.

(a) If we apply positive voltage to the drain electrode, but zero voltage to the gate, we will not achieve any substantial flow of electrons from the source to drain, why?

\_\_\_\_ because the channel will be depleted.

because we will always have at least one reverse biased pn-junction in the way.

\_\_\_\_ magic.

(b) If we apply positive voltage to the drain electrode, and negative voltage to the gate, we would accumulate many holes underneath the gate oxide. This would increase the conductivity of the semiconductor under the gate oxide, but we will still not achieve any substantial flow of electrons from the source to drain, why?

- \_\_\_\_ because the channel will be depleted.

- because we will still have at least one reverse biased pn-junction in the way.

- \_\_\_\_ ghosts.

(c) So now you realize how NOT to turn on an ideal n-channel MOSFET. Recall from the lecture notes that for an n-channel MOSFET we need to apply a positive voltage to gate that is greater than the threshold voltage ( $V_T$ ) to allow flow of electrons from the source to drain. To allow current flow, what happens to the semiconductor near the gate oxide at the threshold voltage?

- \_\_\_\_ it inverts from p-type into n-type, then you have n-type (drain) / n-type (channel) / n-type (source) to allow flow!

- the PN junction at the source or drain becomes forward biased.

- \_\_\_\_ Dancing with the Stars.

(d) So at threshold voltage and above, is there any depletion layer preventing electron flow from source, though the conducting n-channel and to the drain?

- \_\_\_\_\_no, all regions that matter are n-type now!

- \_\_\_\_ yes but it is so thin it does not matter.

- more ghosts.

### (5) Draw:

(a) a simple parallel plate capacitor diagram, and the dielectric material as having 'dipoles' in them like in our slides that can bend or rotate. Explain how charge is propagated through the dielectric and why a positive charge or voltage on one end leads to a negative charge or voltage on the other end....

(b) next draw an electron cloud or spherical electron orbital path around the nucleus of an atom (any simple atom, just draw it simple), keep the positive nucleus fixed in position and applied E-field. Does this create a dipole too? This shows you that you don't need something to actually rotate, any insulating material can capactively propagate a charge through itself.

#### SECS 2077 - Semiconductor Devices Homework

So you know.... materials that have higher permittivity (dielectric constant), simply allow more distortion of their electron clouds and/or in some cases have atomic bonds which can bend or rotate more to create dipoles....

(6) You create some crazy new transistor that is combination JEFT, MESFET, FET, and magical ghosts. The transistors DC drain current response is:  $I_D = V_D(5V_G^2 + 1)$  Calculate the AC (small signal) transconductance for V<sub>G</sub>=1V and V<sub>D</sub>=1V.

Please provide your anonymous feedback. On a paper (such as this) without your name please respond:

(1) What are the top few worst things about this course or the professor?

(2) What are the top few best things about this course or the professor?

(3) Any comments you would like to share in general?